近日,中国科大微电子学院龙世兵教授课题组的五篇论文入选第36届功率半导体器件和集成电路国际会议(IEEE International Symposium on Power Semiconductor Devices and ICs,简称IEEE ISPSD)报告。IEEE ISPSD是功率器件领域最具影响力和规模最大的顶级国际学术会议,被认为是功率半导体器件和集成电路领域的奥林匹克会议,IEEE ISPSD 2024于今年6月2日至6月6日在德国举办。中国科大微电子学院郑柘炀特任教授和徐光伟特任研究员带队参加此次盛会。

图1.参会人员合照:郑柘炀教授(右二),徐光伟研究员(右一)。

本次入选的五篇论文工作如下:

1.氧化镓关键缺陷识别和抑制方法

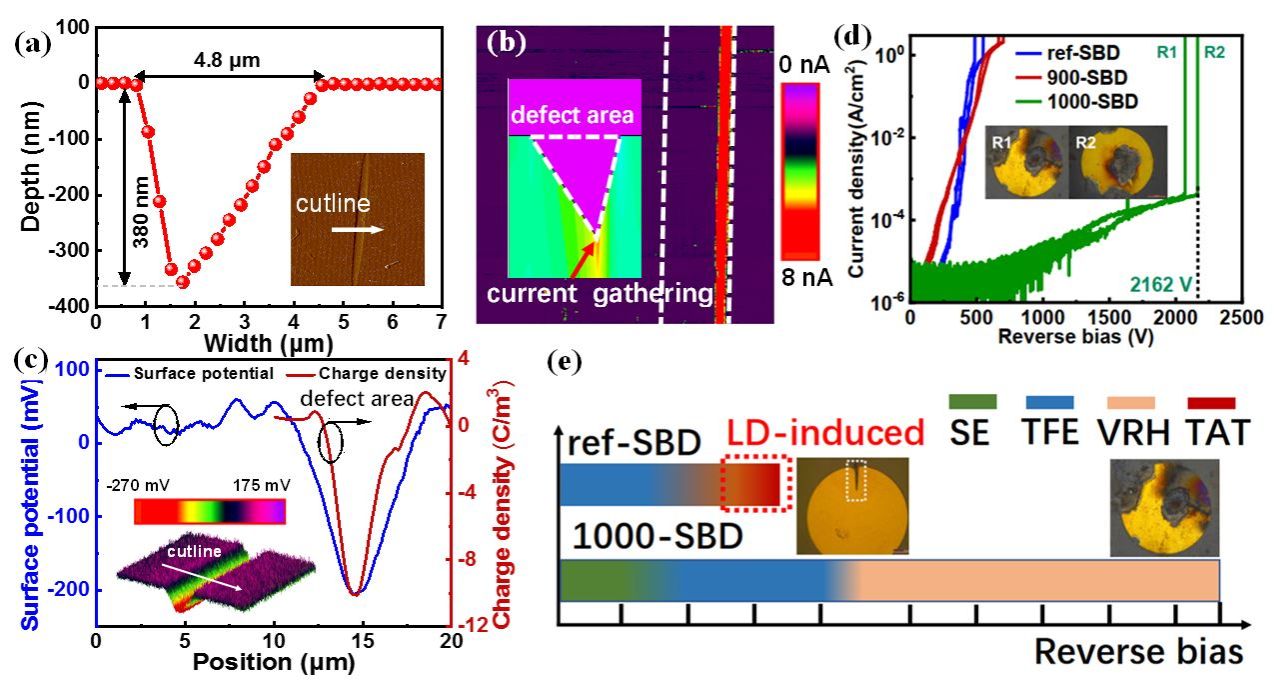

为了制备高耐压氧化镓肖特基势垒二极管(SBD),发挥氧化镓材料的优势,高性能的功率二极管需要在衬底上外延生长低掺杂浓度的外延层作为承压区域。卤化物气相外延(HVPE)的方法结合了生长速度,晶体质量等优势,该方法成为了氧化镓外延生长的重要方式。但是由于生长速度过快,在生长过程中晶体内部容易产生部分无序或者孔洞,这些缺陷可能会对器件性能造成巨大影响。在这项工作中,通过微光显微镜(EMMI)的方式,识别了一种沿着(010)晶向的线型晶格缺陷为一种导致氧化镓SBD提前击穿的关键缺陷(图2)。通过开尔文探针及原子力探针的表征方式,揭示了该缺陷区域的电学特性:固定负电荷的聚集导致电场增大,从而造成漏电增大和提前击穿。此外,研究提出了通过高温氧气退火的方式,成功修复了该缺陷,减少了晶圆上缺陷的数目,并成功制备了高击穿氧化镓SBD。研究成果以“The Role of Line-shaped Defects in Premature Breakdown ofβ-Ga2O3Power Diode and Suppression by Oxygen Annealing”为题作为发表在IEEE ISPSD 2024上并作现场汇报,第一作者为博士生刘金杨。

图2.(a-c)线型缺陷的表面形貌及电学特性,(d)通过氧气退火改善缺陷后的器件击穿特性,(e)优化前后器件的漏电机制对比。

2.低漏电、高耐压的β-Ga2O3异质结势垒肖特基二极管

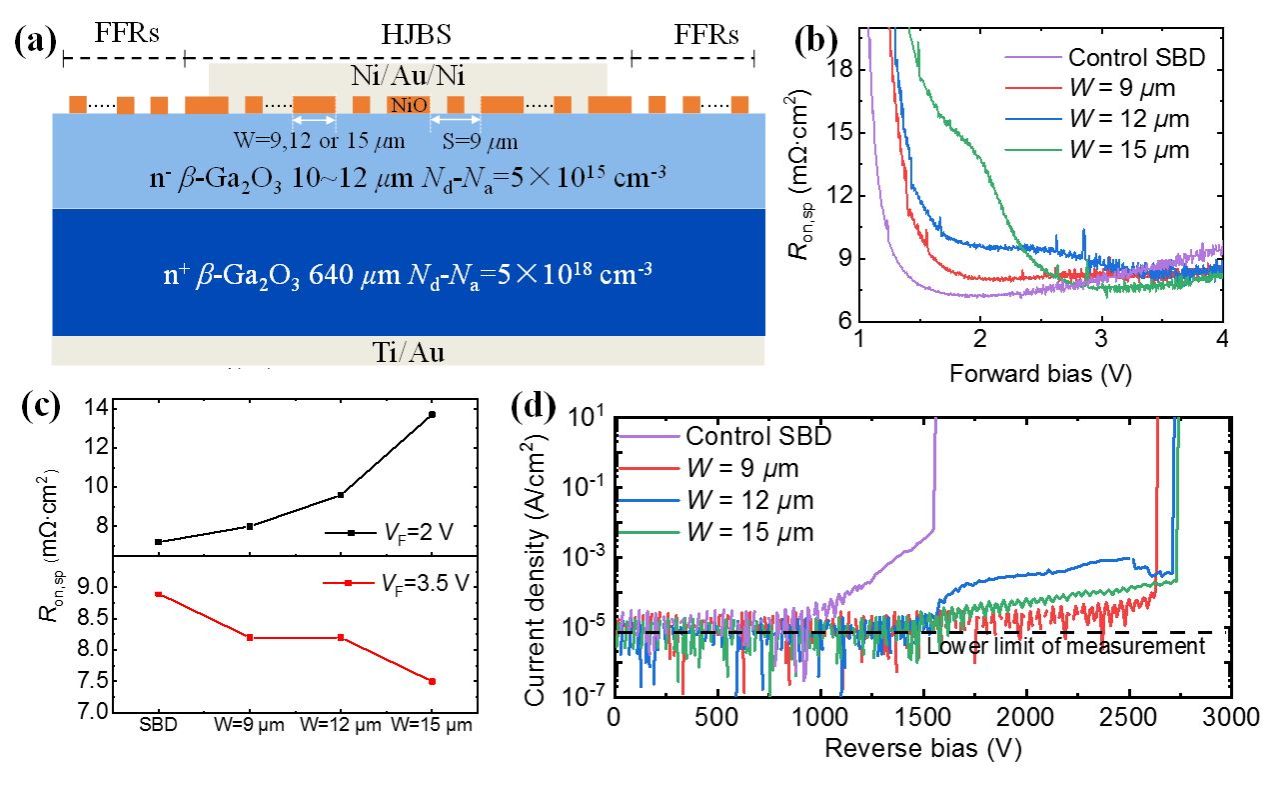

针对高电场下β-Ga2O3SBD器件肖特基结中心区域仍会引起较大的泄漏电流这一问题,引入了降低表面电场(RESURF)技术—结势垒肖特基结构。p-NiO被嵌入到肖特基中心表面以形成p-n结交替排列的β-Ga2O3HJBSD器件。得益于较强的RESURF效应,β-Ga2O3HJBSD器件表现出小于1 mA/cm2的极低的反向泄漏电流,并且击穿电压达到了2.7 kV以上。该β-Ga2O3HJBSD器件成功结合了SBD和HJD器件优势,兼具了低开启电压、低泄漏电流和高击穿电压的优异特性(图3)。研究成果以“2.7 kVβ-Ga2O3Heterojunction Barrier Schottky Diode with Low Leakage Current < 1 mA/cm2Based upon RESURF Effect”为题发表在IEEE ISPSD 2024上,第一作者为博士生郝伟兵。

图3. (a)垂直氧化镓HJBSD器件结构示意图,(b)提取SBD和HJBSDs器件的比导通电阻,(c)分别在正向导通电压2V(异质结导通之前)和3.5V(异质结导通之后)下提取SBD和HJBSDs的导通电阻,(d)SBD和HJBSDs器件的反向击穿特性对比。

3.高耐压氧化镓肖特基势垒二极管研究

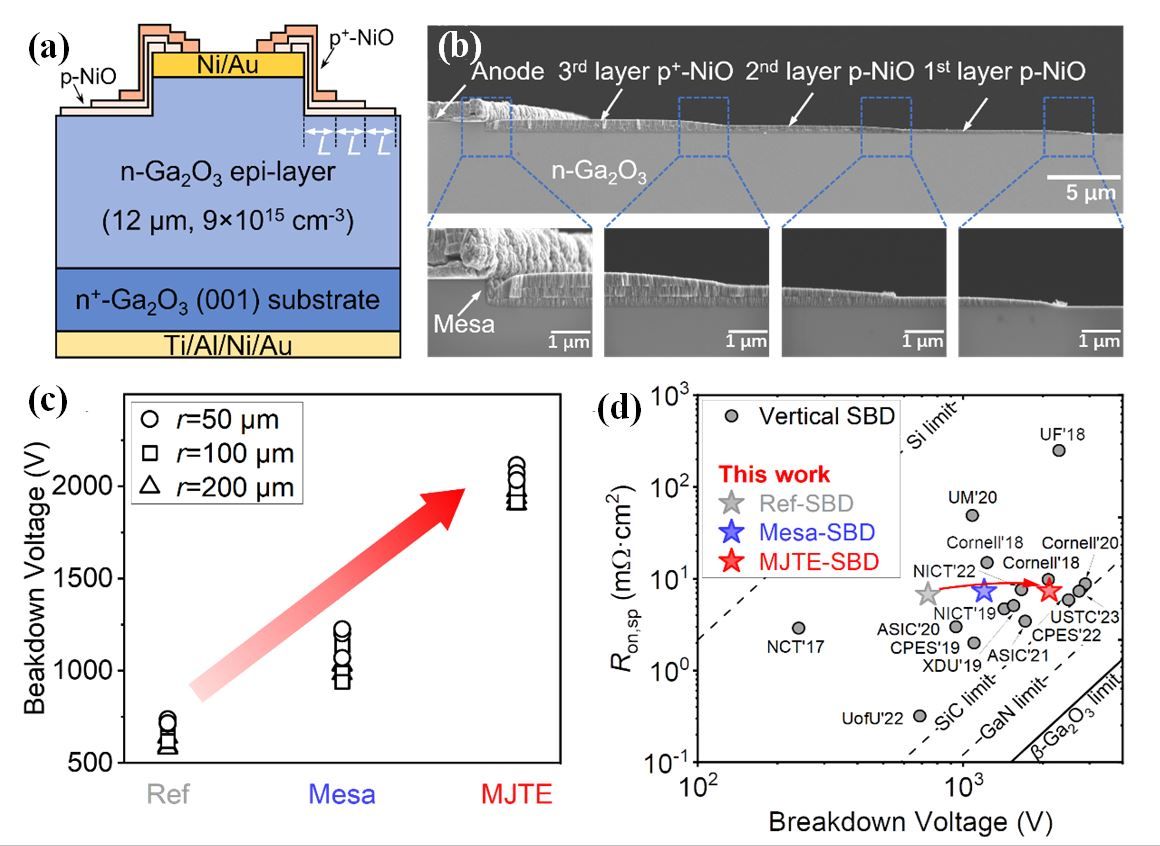

近年来,基于β-Ga2O3的肖特基势垒二极管(SBD)研究迅速发展,并有望率先实现商业化。然而,目前器件的实际性能与理论极限尚有较大差距,有效的边缘终端设计对于提升器件性能至关重要。台面终端(Mesa)能够有效地将SBD边缘柱面结或球面结去除,使得整个器件呈现比较均匀的电场分布。然而,高电场在蚀刻台面侧壁的分布,以及干法刻蚀引起的表面电荷富集,可能存在额外泄漏电流和提前击穿的风险。基于此,课题组设计并制备了具有复合终端的高性能β-Ga2O3SBD(图4)。该复合终端(MJTE)将台面终端和渐变结终端拓展结构(JTE)相结合。台面设计避免了阳极边缘的峰值电场,而渐变多层P型氧化镍(NiO)的设计进一步有效调节了电场分布的梯度。通过TCAD仿真工具,该工作系统研究了电场分布与NiO厚度、台面深度和JTE长度之间的关系。结合优化参数,实际制备器件的击穿电压从738 V提升到2116 V,功率优值(PFOM)提高了七倍(从81.05到608.35 MW/cm2)。这项工作为提高β-Ga2O3SBD的性能提供了切实有效的解决方案。研究成果以“Improvedβ-Ga2O3Schottky Barrier Diodes Featuring p-NiO Gradual Junction Termination Extension within Mesa Structure”为题发表在IEEE ISPSD 2024上,第一作者为博士生韩照。

图4.(a)设计的β-Ga2O3MJTE-SBD器件结构示意图,(b)制备器件的扫描电子显微镜图像,(c)器件击穿特性统计分布结果,(d)该工作器件与国际已报道器件的性能对比。

4.低栅漏电氧化镓pn结-异质结场效应晶体管

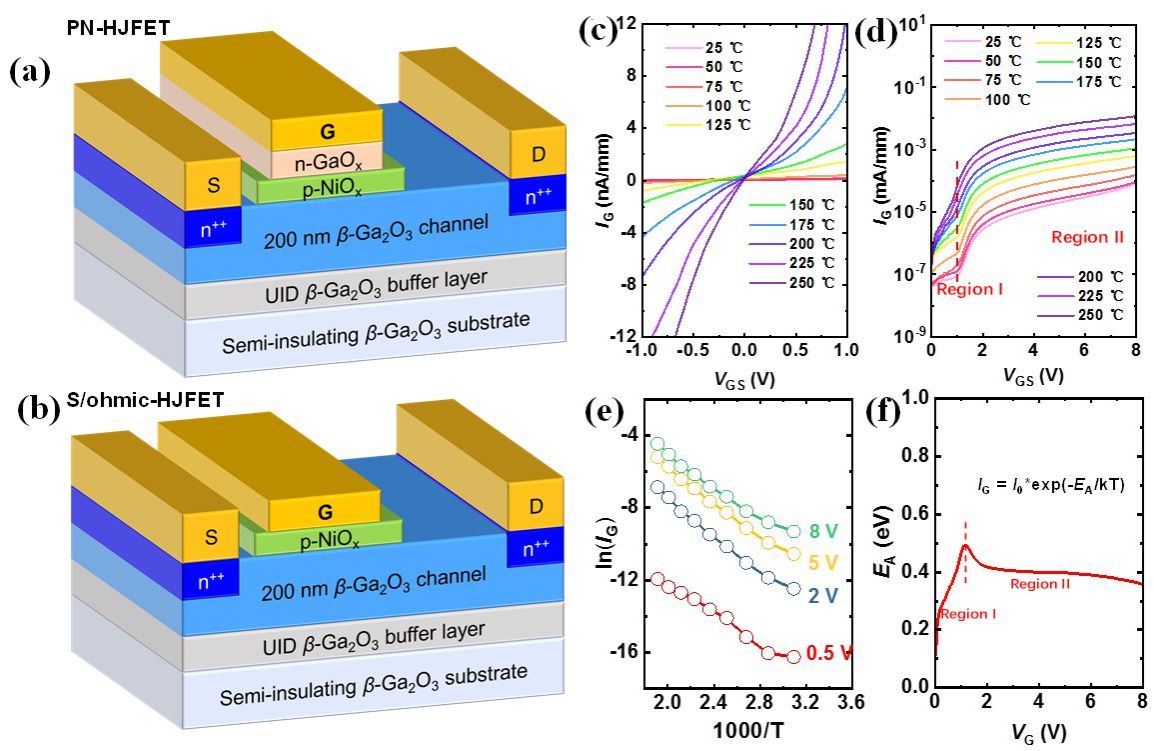

基于p-NiO的β-Ga2O3异质结场效应晶体管在高功率和高频开关应用中显示出巨大潜力。然而在先前的研究中,基于p-NiO的β-Ga2O3异质结场效应晶体管存在寄生的栅源pn二极管,导致较大的栅极漏电电流,促使需要创新的解决方案。该工作中,针对β-Ga2O3异质结场效应晶体管(HJFET)的栅极击穿问题,通过引入NiOx/GaOx栅极堆叠结构,成功设计并制备了一种新型的pn结-异质结场效应晶体管PNJ-HJFET。这种结构显著提高了栅极击穿电压至14.2 V。PNJ-HJFET在25至250 ℃的宽温度范围内,表现出了优异的稳定性和极低的阈值电压偏移(图5)。此外,通过分析栅极漏电特性,揭示了PNJ-HJFET在不同温度下的导电机制,为β-Ga2O3HJFETs的栅极击穿问题提供了一种有效的解决方案。研究成果以“Enhanced Gate Breakdown inβ-Ga2O3HJFET through a NiOx/GaOxp-n Junction Gate Stack”为题发表在IEEE ISPSD 2024上,第一作者为博士后周选择。

图5.(a)氧化镓PN-HJFET器件和(b)氧化镓S/ohmic-HJFET器件结构示意图,(c)PN-HJFET器件的栅极电流-电压(IG-VG)特性,(d)在温度范围25-250℃下测量的PN-HJFET器件的栅极电流-电压特性,(e)IG-1000/T的Arrhenius曲线,(f)从图(e)提取的激活能EA。

5.千伏级氮离子注入氧化镓垂直晶体管

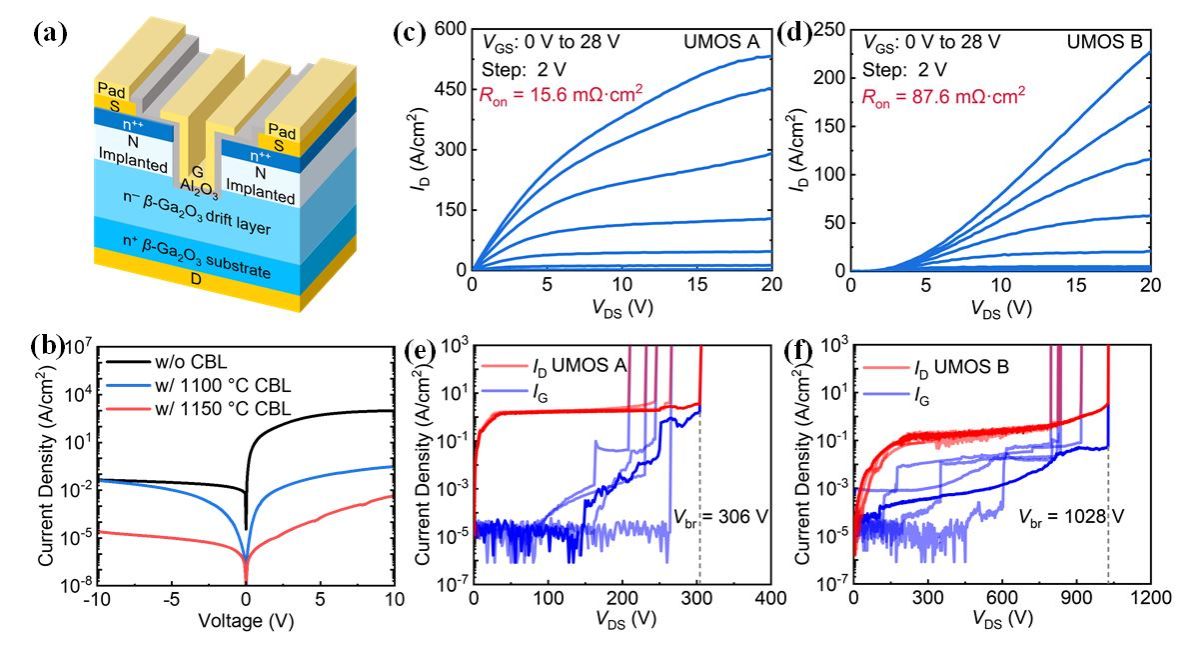

由于p型氧化镓的实现极具挑战,这在一定程度上限制了氧化镓增强型晶体管的实现方案。而受主掺杂可补偿氧化镓中的载流子,在氧化镓材料中实现电流阻挡层,这为实现增强型场效应晶体管提供了新的思路。氧化镓中形成电流阻挡层的主流方法包括氧气氛围高温退火、镁元素掺杂及氮元素掺杂。但在目前的研究中,电流阻挡层的漏电特性仍不理想,导致器件在关断状态下泄漏电流较高,容易造成器件的提前击穿。该工作采用氮离子注入的方法实现了电流阻挡层,并通过优化离子注入后的退火激活温度抑制了电流阻挡层的漏电。基于优化后的离子注入后退火工艺,该工作实现了击穿电压高于1 kV的U型槽栅垂直晶体管,与优化前的器件相比,其击穿电压有显著提高,初步展示了基于电流阻挡层的氧化镓垂直晶体管的潜力,如图6所示。研究成果以“1-kVβ-Ga2O3UMOSFET with Quasi-Inversion Nitrogen-Ion-Implanted Channel”为题发表在IEEE ISPSD 2024上,并获得大会唯一最佳海报奖(Best Poster Award),见图7,博士生刘琦和博士后周选择为该论文共同第一作者。

图6.(a)β-Ga2O3UMOSFET器件结构示意图,(b)不带电流阻挡层(CBL)和分别在1100℃、1150℃下退火的带CBL的测试结构的电流-电压特性,(c)UMOS A(1100℃退火)和(d)UMOSB(1150℃退火)器件的脉冲输出特性,(e)UMOS A(1100℃退火)和(f)UMOSB(1150℃退火)器件的击穿特性。

图7. 我校博士生刘琦获奖(最佳海报奖)颁奖现场。

以上五项研究成果得到了国家自然科学基金、中国科学院、科技委、广东省重点领域研究发展计划、中国科学技术大学青年创新重点项目的资助,同时得到了中国科学技术大学微纳研究与制造中心、信息科学实验中心的支持。

(微电子学院)